# **High Performance Silicon IP Solutions**

# **ntADPCM**

G.726 Source Codec

The ntADPCM core is fully compliant with G.726 standard and supports up to 64 full duplex voice channels. The G.726 recommendations specifies the conversion of a 64 kbps A-law or  $\mu$ -law pulse code modulation (PCM) to and from a 40, 32, 24 and 16 kbps channel. This conversion is applied to the PCM bit stream using an ADPCM transcoding technique. The ntADPCM core can be configured 'on-the-fly' for A-law or  $\mu$ -law linear code and conversion rate on a per channel basis.

The core is used in applications that require reduction in transport and storage bandwidth requirements. It significantly offloads CPU tasks as a co-processing system element.

## **Applications**

The ntADPCM core can be used in a variety of applications, including:

- Cordless handsets and base stations (DECT, CT2, Cellular).

- Integrated Access Devices.

- PBX's (Private Branch Exchange).

- Voice storage, voice mail, WAN voice processing.

- DCME (ITU G.763).

- Variable bandwidth channel.

- DSL modem, Cable modem, DSLAM.

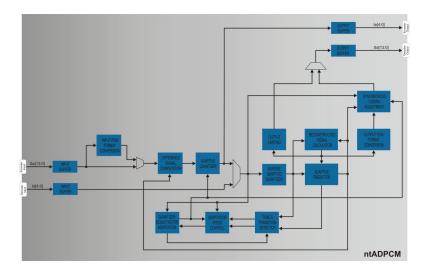

# **Block Diagram**

#### **Features**

- Compliant with ITU G.721, G.723, G.726 and G.726-Annex recommendations.

- $\bullet$  'On-the-fly' configuration for variable compression rate, PCM law.

- Process capability of up to 64 full duplex or up to 128 half duplex voice channels.

- Burst and continuous mode support.

- No register based configuration is required.

- A-law, µ-law linear code format selection.

## **Implementation results**

The core has been targeted to both ASIC and FPGA technologies for various applications. Noesis Technologies can also deliver netlist versions of the core optimized to specific area resources and performance requirements.

| Silicon<br>Vendor | Device     | Resources <sup>1</sup> | Fmax<br>(MHz) |

|-------------------|------------|------------------------|---------------|

| Xilinx            | Virtex -II | 2515 CLB Slices        | 60            |

| TSMC              | 0.18 um    | 24K gates <sup>1</sup> | 200           |

1. Equivalent NAND2 gate count.

#### **Deliverables**

Noesis has engaged an "open" licensing philosophy in order to allow maximum technology transfer to our client's engineering teams and to facilitate the integration of our IP cores into our client's product. Various licensing models are available. The ntADPCM core is available as a soft core (synthesizable HDL) or as a firm core (netlist for FPGA technologies). The following deliverables are included:

- Fully commented synthesizable VHDL or Verilog source code or FPGA netlist.

- $\bullet$  VHDL or Verilog test benches and example configuration files.

- C source code.

- Comprehensive technical documentation.

- Technical support.

#### Support

Technical support by phone or email is included. First year of maintenance is also included. Additional support and annual maintenance options are available.

## **Ordering information**

To purchase or make any further inquiries about our ntADPCM core, or any other Noesis Technologies products or services, contact us at <a href="mailto:info@noesis-tech.com">info@noesis-tech.com</a>. Noesis Technologies products are purchased under a License Agreement, copies of which are available on request.

Noesis Technologies L.P. Patras Science Park Stadiou Rd, Platani Rion GR-26504 - Patras GREECE

Phone: +30 2610 911531 Email: info@noesis-tech.com