# ntFFT

# Fully Configurable Radix-2 FFT/IFFT Processor

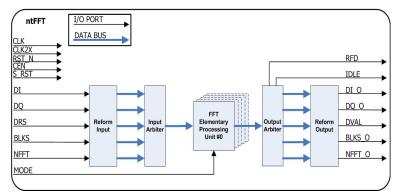

ntFFT core is a fully configurable solution that performs the FFT and IFFT transform. It is on-the-fly programmable in terms of transform size and type. It supports complex input/output and the results are output in normal order. It exhibits a highly parameterizable/scalable design using generic I/O fixed point precision and generic internal calculations precision. The core uses fixed-point 2's complement arithmetic with internal auto scaling to avoid arithmetic overflow and simplify dynamic range management. The ntFFT IP Core employs a revolutionary parameterized architecture where the user can fine tune the level of data-path parallelism in order to achieve the optimum trade-off between silicon resources and throughput rate. The implementation is portable to various silicon technologies, with a simple interface for easy integration in SoC applications.

## **Applications**

The ntFFT core can be used in a variety of applications, including:

- Communication Systems.

- Spectrum Analysis.

- OFDM modems.

- Image processing.

- Defense Receivers and Signal Monitoring.

- Medical and Scientific Instruments.

#### **Features**

- Radix-2 Fast Fourier Transform processor IP Core.

- Same IP core may be used to compute both FFT and IFFT transforms without any complexity overhead.

- Highly parameterizable/scalable design using generic I/O fixed point precision and generic internal calculations precision.

- Bit true Matlab script model is provided to aid core fixed point precision configuration for any target application.

Tested against Matlab FFT and IFFT functions the ntFFT core pro-

- Tested against Matlab FFT and IFFT functions the ntFFT core produces fixed point numerical results with mean absolute error in range of 1e-4. The core may be parameterized for greater internal fixed point precision to lower the mean absolute error further.

- Final fixed point scaling to avoid precision loss is performed internally.

- Highly programmable design supporting all power of 2 FFT/IFFT transforms in range [8,...,MAX\_NFFT], where MAX\_NFFT=[8, ...,8192]. Support for any power of 2 higher than 8192 is also possible

- Parameterized architectural parallelism level to meet any target application by tuning an efficient trade-off between utilized resources and maximum throughput rate.

- Overclocked main memory at 2x rate to achieve minimum memory resources utilization.

- Simple yet robust interface for optimum and efficient data flow control.

- Optional AXI4-Stream protocol interface support.

- Synchronous clock design.

- Silicon proven in ASIC and FPGA technologies for a variety of applications.

## **Implementation results**

The core has been targeted to both ASIC and FPGA technologies for various applications. Noesis Technologies can also deliver netlist versions of the core optimized to specific area resources and performance requirements.

| FFT<br>size | Resources<br>Xilinx Kintex-7 Device                 | Fmax<br>(MHz) |

|-------------|-----------------------------------------------------|---------------|

| 128         | 547 CLB Slices /<br>4 Block RAMs / 8 DSP48 Blocks   | 206           |

| 512         | 716 CLB Slices /<br>5 Block RAMs / 8 DSP48 Blocks   | 190           |

| 1024        | 652 CLB Slices /<br>6 Block RAMs / 12 DSP48 Blocks  | 171           |

| 2048        | 765 CLB Slices /<br>16 Block RAMs / 16 DSP48 Blocks | 170           |

| 4096        | 745 CLB Slices/<br>16 Block RAMs / 16 DSP48 Blocks  | 170           |

| 8192        | 836 CLB Slices/<br>33 Block RAMs / 16 DSP48 Blocks  | 166           |

# **Deliverables**

Noesis has engaged an "open" licensing philosophy in order to allow maximum technology transfer to our client's engineering teams and to facilitate the integration of our IP cores into our client's product. Various licensing models are available. The ntFFT core is available as a soft core (synthesizable HDL) or as a firm core (netlist for FPGA technologies). The following deliverables are included:

- Fully commented synthesizable VHDL or Verilog source code or FPGA netlist.

- $\bullet$  VHDL or Verilog test benches and example configuration files.

- Matlab code.

- Comprehensive technical documentation.

- Technical support.

#### Support

Technical support by phone or email is included. First year of maintenance is also included. Additional support and annual maintenance options are available.

#### **Ordering information**

To purchase or make any further inquiries about our ntFFT core, or any other Noesis Technologies products or services, contact us at <a href="mailto:info@noesis-tech.com">info@noesis-tech.com</a>. Noesis Technologies products are purchased under a License Agreement, copies of which are available on request.

Noesis Technologies P.C. Patras Science Park Stadiou Rd, Platani Rion GR-26504 - Patras GREECE Phone: +30 2610 911531

Phone: +30 2610 911531 Email: info@noesis-tech.com