## **High Performance Silicon IP Solutions**

# ntHDLC

Noesis Technologies ntHDLC single channel High-Level Data Link Controller (HDLC) is a full-duplex transceiver with independent transmit and receive units for synchronous framing bit-level HDLC protocol operations. The ntHDLC can handle interframe and delimiting flags, frame check sequence based on CCITT CRC16/CRC32 polynomial, normal or transparent transmission modes, abort generation and detection. The system interface is very flexible and can be adapted towards FIFO, uP, or DMA controllers. The transmit and receive units and their associated control and status logic are independent. This partitioning strategy enables the Tx and Rx units to be instantiated in different place and/or level of the design hierarchy. Each unit (Tx, Rx and back-end interface) has its own clock domain with synchronous clock enable. Communication between the various clock domains is achieved via synchronization logic blocks.

The ntHDLC core can be used in a variety of applications, including:

- Embedded applications in Telecom systems.

- X.25 (LAPB), Q.921(LAPD) applications.

- Point to point communication links.

- ISDN, Q.922 Frame Relay, PBX, WAN.

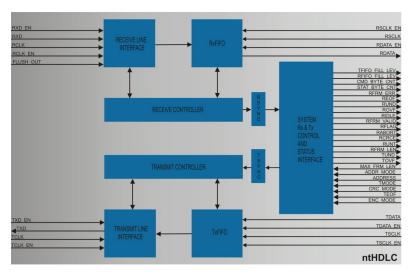

## **Block Diagram**

- Single port synchronous serial line interface.

- Flag/Abort Generation/Detection.

- Zero Insertion/Deletion.

- Non-octet alignment detection.

- CCITT CRC-16 Generation and Checking.

- NRZ/NRZI encoding/decoding.

- Transparent mode support.

- Receive FIFO overrun detection.

- Transmit FIFO underrun detection.

- Frame status and frame length indicators.

- Runt frame detection.

- Seperate clocks for Tx and RX interfaces.

- Supports fllag in interframe-time fill.

- 8-bit parallel back-end interface.

- Fully synchronous design.

- Silicon proven in ASIC and FPGA technologies for a variety of applications.

Noesis Technologies L.P. Patras Science Park Stadiou Rd, Platani Rion

Phone: +30 2610 911531 Email: info@noesis-tech.com

GR-26504 - Patras

**GREECE**

# Single Channel HDLC Controller

## Implementation results

The core has been targeted to both ASIC and FPGA technologies for various applications. Noesis Technologies can also deliver netlist versions of the core optimized to specific area resources and performance requirements.

| Silicon<br>Vendor | Device      | Resources <sup>1</sup>                     | Fmax<br>(MHz)                                          |

|-------------------|-------------|--------------------------------------------|--------------------------------------------------------|

| Xilinx            | Spartan 3   | 460 CLB<br>Slices /<br>10 Block<br>RAMs    | 80 (tclk)<br>126 (rclk)<br>140 (tsclk)<br>140 (rsclk)  |

| Xilinx            | Virtex 5    | 200 CLB<br>Slices /<br>10 Block<br>RAMs    | 130 (tclk)<br>230 (rclk)<br>310 (tsclk)<br>313 (rsclk) |

| Altera            | Stratix-III | 600 ALUTs /<br>10 M9K RAM<br>blocks        | 72 (tclk)<br>139 (rclk)<br>184 (tsclk)<br>133 (rsclk)  |

| TSMC              | 0.18 um     | 5800 gates <sup>2</sup> /<br>74 K RAM bits | 340 (tclk)<br>400 (rclk)<br>330 (tsclk)<br>340 (rsclk) |

- 1. The implementation uses 2 FIFOs of 4096 words x 9 bits/word size each. Please contact us to provide results for different FIFO size implementations.

- 2. Equivalent NAND2 gate count.

## **Deliverables**

Noesis has engaged an "open" licensing philosophy in order to allow maximum technology transfer to our client's engineering teams and to facilitate the integration of our IP cores into our client's product. Various licensing models are available. The ntHDLC core is available as a soft core (synthesizable HDL) or as a firm core (netlist for FPGA technologies). The following deliverables are included:

- Fully commented synthesizable VHDL or Verilog source code or FPGA netlist.

- VHDL or Verilog test benches and example configuration files.

- Comprehensive technical documentation.

- Technical support.

### Support

Technical support by phone or email is included. First year of maintenance is also included. Additional support and annual maintenance options are available.

### **Ordering information**

To purchase or make any further inquiries about our ntHDLC core, or any other Noesis Technologies products or services, contact us at <a href="mailto:info@noesis-tech.com">info@noesis-tech.com</a>. Noesis Technologies products are purchased under a License Agreement, copies of which are available on request.

www.noesis-tech.com